Temat: [Atari 65XE, układ Freddy] Naprawa, proteza CPLD

Mam w naprawie Atari 65XE. Po przeanalizowaiu każdego scalaka doszedłem do wniosku, że:

* Dekoder PAL jest uszkodzony - wymieniłem na GALa zaprogramowanego odpowiednim wsadem (swoją drogą ciekawe, bo już raz trafiłem na taką usterkę)

* Układ FREDDIe jest uszkodzony - tutaj też ciekawe, że tylko ten jeden układ jest w podstawce (przewidzieli na etapie produkcji, że często padają?)

Reszta sprawna, zamieniając na sprawnego FREDDYego z innej konsoli - atari ożyło. Jednak tego scalaka widzę nie da się dostać, więc postanowiłem go czymś zastąpić.

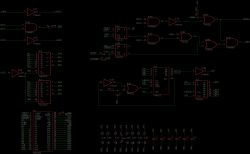

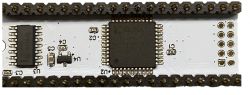

Widzę są rożne projekty wymiany go albo na wersję opartą o CPLD:

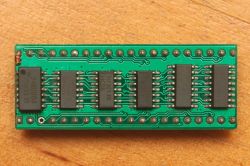

Albo na rekonstrukcję na układach 74XX:

Jako że mam trochę doświaczenia z CPLD to postanowiłęm wykorzystać układ EPM3064 których mam na pęczki. Trafiłem na strone opisującą zachowanie tego scalaka:

https://hardware.atari8.info/freddie.php

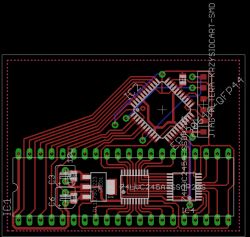

Więc zaprojektowałem sobie dedykowaną plytkę drukowaną, wytrafiłem, polutowałem i wbudowałem go do konsoli (ponieważ EPM3064 nie ma wystarczająco dużo pinów, aby wszystko obsłużyć, do multipleksacji A0..A7 i A8..A15 użyłem dwóch buforów 74LVC245

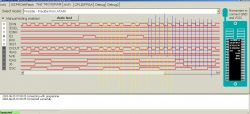

Oprogramowałem wsadem z powyższej strony. Jakież było moje zdziwienie, gdy konsola nie dała żadnych oznak życia, nie pojawil się nawet sygnał OSC ani PHI2.

Szczerze mowiąc, troche nie rozumiem czemu ten licznik liczy w kolejności:

0,1,3,2,6,7,5,4

oraz dlaczego korzysta z sygnału PHI2 w funkcji przejścia. Widać winowajcą okazała się część z PHI2 w tym kodzie:

fcount(0) <=

(not fcount(2) and not fcount(1) and not phi2)

or (fcount(2) and fcount(1) and phi2);

fcount(1) <=

(not fcount(2) and fcount(0) and not phi2)

or (not fcount(2) and fcount(1) and not fcount(0) and not phi2)

or (fcount(2) and fcount(1) and not fcount(0) and phi2);

fcount(2) <=

(not fcount(2) and fcount(1) and not fcount(0) and not phi2)

or (fcount(2) and fcount(1) and not fcount(0) and phi2)

or (fcount(2) and fcount(0) and phi2);Po wywaleniu "phi2" z funkcji logicznej, wreszcie pojawiło się i OSC i PHI2:

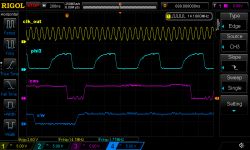

Niestety konsola nadal nie działa prawidłowo - albo na ekranie pojawiają sie jakieś śmieci, albo ekran jest czarny, raz na kilkanaście uruchomień pojawia sie niebieski ekran z READY jak w działającej konsoli, jednak kolory wyraźnie nie były stabilne.

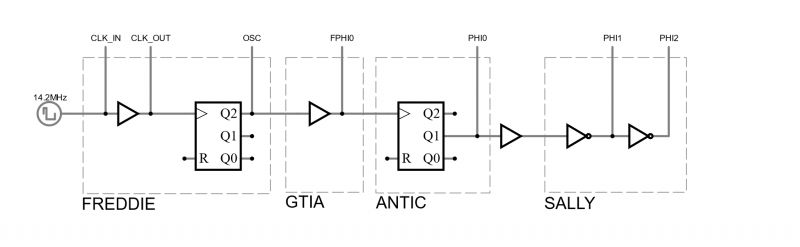

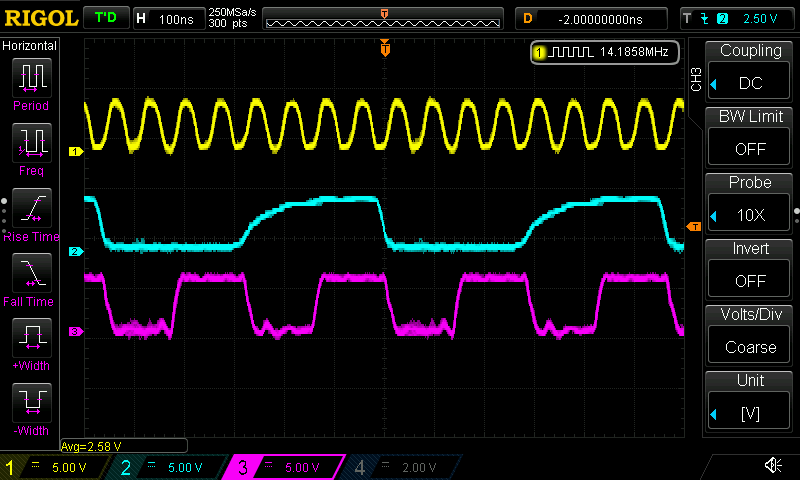

Z tego co widzę wg schematu tego atari, CLK_IN oraz CLK_OUT we freddy-m to po prostu negator, który służy do wprowadzenia kwarcu 14 MHZ w drgania. Ponieważ sygnał zegarowy byl mocno koślawy, pomyślałem że negator w CPLD słabo sobie radzi w tej roli. Podłączyłem więc zamiast tego układ 74HCU04 (dedykowany negator do zatosowań zegarowych) i teraz faktycznie, raz na te kilkanaście uruchomień jak pojawi sie ekran z READY to kolory są stabilne, zegar ma ładne zbocza (nie licząc tych overshootów), jednak dlaczego konsola w wiekszości razy po uruchomieniu nie działa?

Czemu w ogóle według tej strony przebiegi powinny być takie (np PHI2 rośnie i opada na rosnącym zboczu OSC)

a na działającym freddym są takie (rośnie i opada na opadającym zboczu OSC)

czyli takie same jak na mojej CPLDowej protezie.

Ma ktoś DZIAŁAJĄCY model VHDL tego układu bo już mnie krew zalewa. Przeszukałem pól sieci i nic nie znalazłem, jakby to był jakiś top-secret układ.

Ostatnio edytowany przez krzysiobal (2023-08-22 16:23:44)