Hej!

Co do przycisku i przełącznika. To typowy cart T2000 który odłącza się po pewnym czasie od momentu włączenia zasilania za pomocą prostego czasowego zbudowanego z tranzystora, diody, dwóch rezystorów i kondensatora. Stała czasowa układu R/C określa po jakim czasie układ wyłączy się (po naładowaniu kondensatora). Przycisk widoczny na zdjęciu powoduje ponowne włączenie carta poprzez zwykłe zwarcie wyprowadzeń kondensatora razem (rozładowanie go). Wystarczy wcisnąć ten przycisk i RESET aby cartridge został ponownie wykryty i uruchomiony przez system.

Co do przełącznika ON/OFF, no zamierzeniem autora tego rozwiązania było zapewne całkowite odłączenie cartridge po przełączeniu przełącznika z pozycję OFF, jednak autor pomysłu popełnił fundamentalny błąd. Przełącznik odłącza jedynie napięcie zasilania od pamięci EPROM (VCC, PIN 24). Efekt jest taki iż układ RC cały czas działa a więc system normalnie może wykryć (TRIG3) iż cart jest włożony i aktywny, jednak zamiast zawartości pamięci EPROM (gdy ta jest zasilana) w przypadku tej pamięci EPROM (VCC=0), na szynie danych (D0-D7) pojawiają się stany które CPU odczytuje jako same logiczne '1'. Pamięć EPROM zostaje normalnie mapowana w adresach $A000-$BFFF i OS próbuje uruchomić cart którego nagłówek ($BFFA-$BFFF) to same $FF. Rozwiązanie to bardzo mało eleganckie i znam powodów jakimi kierował się jego autor, wystarczyło odcinać RD5 i po sprawie CART pozostał by odłączony. Czemu zastosowano taka prowizorkę nie wiem, ale sądzę że pozostawienie VCC "wiszącego w powietrzu", gdy inne linie pamięci EPROM są normalnie wpięte w magistralę to jest całkiem zły i fatalny pomysł :P

Nie mam teraz pod ręką ATARI ze zwykłym OS (tylko QMEG), po przełączeniu przełącznika na OFF i włączeniu komputera efekt jest taki że QMEG startuje ze swoim MENU i statusem "CAR", po chwili cart się odłącza i można pracować normanie. Zakładam iż zwykły fabryczny OS-ROM przechodził w tym momencie do SELF-TEST.

dla zilustrowania przykładowe fotki (na ekranie widać obszar pamięci zaczynający się od $A000):

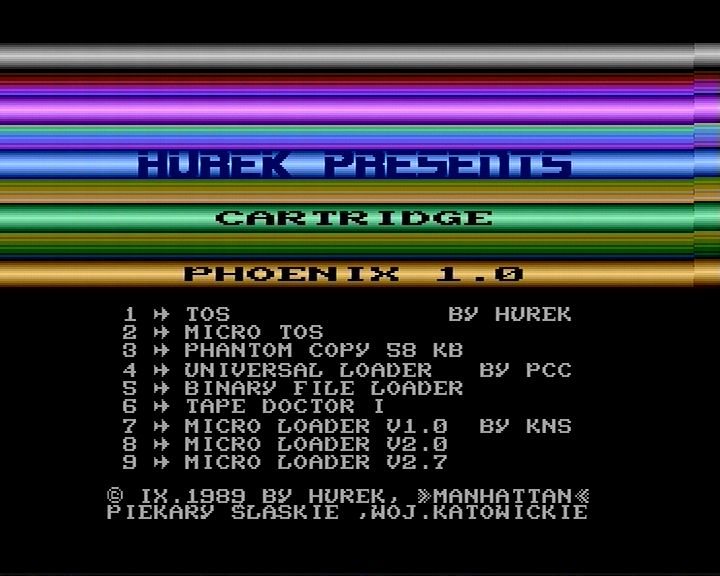

przełącznik w pozycji ON:

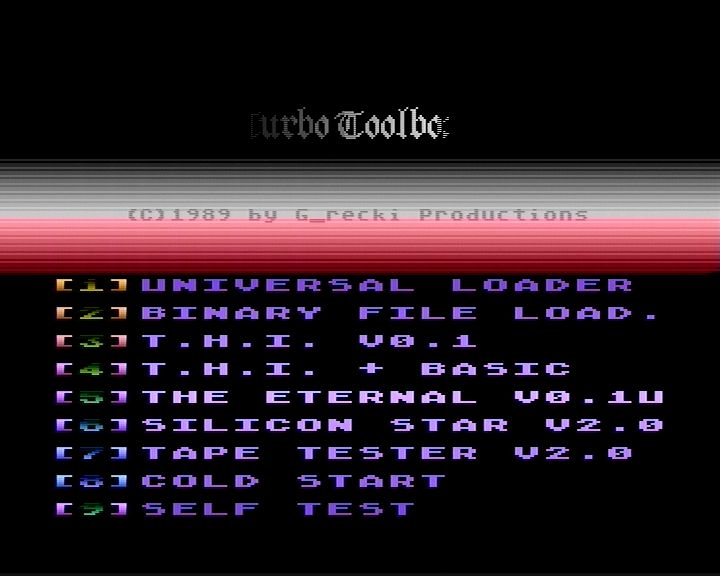

przełącznik w pozycji OFF:

ekran po włączeniu komputera przy przełączniku w pozycji OFF (QMEG-OS):